# PRINTED WIRING BOARD DESIGN FOR MANUFACTURABILITY GUIDELINES

Created by the HADCO Product Engineering and Field Application Engineering Teams.

Copyright 1999 HADCO Corporation

All rights reserved. No part of this document that is covered by copyrights hereon may be reproduced or used in any form or by any means – graphic, electronic, or mechanical, including photocopying, recording, or taping, or information storage and retrieval systems – without written permission of HADCO Corporation.

Document Number: 3001W26.02 Revision: 1.2

Printed in the United States of America

http://www.hadco.com

The team encourages feedback about this document. E-mail <u>dfm\_guide@hadco.com</u> with suggestions.

# **TABLE OF CONTENTS**

| INTRODUCTION                                        | <u>1</u> |

|-----------------------------------------------------|----------|

| HADCO SALES AND TECHNICAL SUPPORT LOCATIONS         | 2        |

| HADCO MANUFACTURING AND DESIGN FACILITIES           | 3        |

| PANEL UTILIZATION                                   | 4        |

| PANEL UTILIZATION TUTORIAL                          |          |

| STEP-AND-REPEAT                                     |          |

| CONTROLLED IMPEDANCE COUPONS                        |          |

| ASSEMBLY RAILS                                      |          |

| ASSEMBLY ARRAYS OR SUB-PANELS                       |          |

| PANEL UTILIZATION DESIGN GUIDELINES                 |          |

| STANDARD PANEL SIZES                                |          |

| MATERIALS AND LAYER STACKUP                         |          |

| MATERIALS & LAYER STACKUP TUTORIAL                  |          |

| MATERIALS                                           |          |

| LAYER STACKUP                                       | 9        |

| MATERIAL DESIGN GUIDELINES                          | 10       |

| FR4 MATERIAL TOLERANCES                             | 10       |

| MULTILAYER CONSTRUCTION DESIGN GUIDELINES           | 11       |

| STANDARD PWB CONSTRUCTIONS                          | 12       |

| BURIED CAPACITANCE <sup>TM</sup> DESIGN GUIDELINES  | 16       |

| CAPACITANCE WITHOUT CAPACITORS                      | 16       |

| PREFERRED BURIED CAPACITANCE CONSTRUCTIONS          | 16       |

| TRACES, PADS & CONDUCTIVE FEATURES                  | 18       |

| TRACES, PADS & CONDUCTIVE FEATURES TUTORIAL         | 18       |

| LINE WIDTH AND SPACE                                | 18       |

| THIEVING                                            | 18       |

| PADS, DRILLED HOLES AND POWER PLANE CLEARANCE       |          |

| ANNULAR RING                                        |          |

| NON-FUNCTIONAL PAD REMOVAL                          | 20       |

| TEARDROPPING                                        | 20       |

| CIRCUIT TO PAD CONNECTIONS                          | 20       |

| DANGLING TRACES                                     | 21       |

| SPACING                                             | 21       |

| LINE WIDTHS                                         | 22       |

| POWER PLANE CLEARANCE AND THERMAL PADS              | 22       |

| CLEARANCE PADS                                      | 23       |

| DIRECT CONNECT VIAS (NO THERMAL PAD)                | 24       |

| VOLTAGE PLANE SEPARATION                            | 24       |

| CROSSHATCH                                          | 25       |

| COPPER IN CUTOUTS AND LOW PRESSURE AREAS            | 26       |

| TRACES, PADS & CONDUCTIVE FEATURE DESIGN GUIDELINES | 28       |

| GENERAL                                             |          |

| INTERNAL POWER / GROUND LAYER DESIGN GUIDELINES     | 28       |

| INTERNAL SIGNAL LAYER DESIGN GUIDELINES             | 29       |

# HADCO

| OUTER SIGNAL LAYER DESIGN GUIDELINES                                          | 29         |

|-------------------------------------------------------------------------------|------------|

| DRILLED HOLES & SLOTS                                                         | 31         |

| DRILLED HOLES & SLOTS TUTORIAL                                                | 31         |

| PLATED THROUGH HOLES<br>OPTIONALLY PLATED THROUGH HOLES<br>GENERAL GUIDELINES |            |

| ASPECT RATIO<br>HOLE TO HOLE SPACING<br>ROUTED VERSUS DRILLED HOLES           | 32         |

| DRILLED HOLES & SLOTS DESIGN GUIDELINES                                       |            |

| GENERAL                                                                       |            |

| NON-PLATED THROUGH HOLES                                                      |            |

| PLATED THROUGH HOLES                                                          |            |

| NON-PLATED THROUGH SLOTS                                                      |            |

| PLATED SLOTS                                                                  |            |

| STANDARD DRILL SIZES                                                          |            |

| SOLDERMASK                                                                    |            |

| SOLDERMASK TUTORIAL                                                           |            |

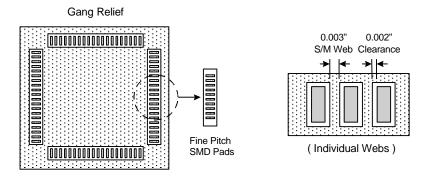

| WEBBING                                                                       |            |

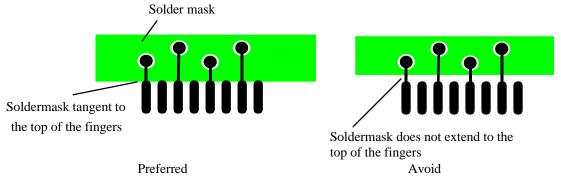

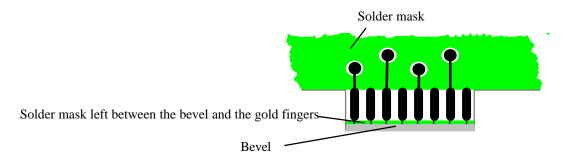

| SOLDERMASK ON THE TOP OF GOLD EDGE FINGERS                                    |            |

| SOLDERMASK AT THE BOTTOM OF GOLD EDGE FINGERS                                 |            |

| Soldermask Design Guidelines                                                  |            |

| LEGEND                                                                        |            |

| LEGEND TUTORIAL                                                               |            |

| LEGEND DESIGN GUIDELINES                                                      |            |

| MECHANICAL FEATURES                                                           | 40         |

| MECHANICAL FEATURES TUTORIAL                                                  | 40         |

| ROUTING                                                                       |            |

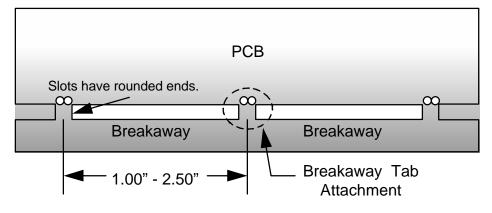

| BREAKAWAY RAILS                                                               | 40         |

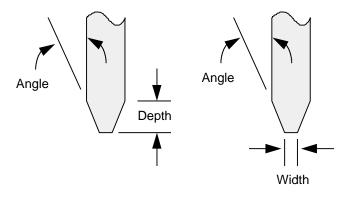

| BEVELING                                                                      |            |

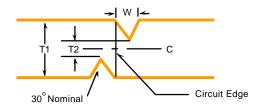

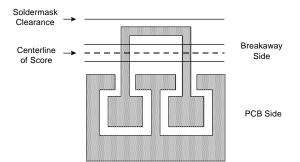

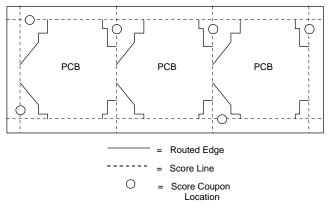

| SCORING                                                                       |            |

| EDGE MILLING                                                                  |            |

| MECHANICAL FEATURES DESIGN GUIDELINES                                         |            |

| ROUTING<br>BREAKAWAY RAILS                                                    |            |

| BEVELING                                                                      |            |

| SCORING                                                                       |            |

| EDGE MILLING                                                                  |            |

| SURFACE FINISHES                                                              | <u>4</u> 5 |

| SURFACE FINISHES TUTORIAL                                                     |            |

| SOLDERABLE FINISHES                                                           |            |

| MECHANICAL MOUNTING SURFACES                                                  | 45         |

ii

# HADCO

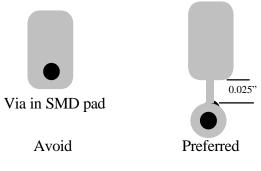

| VIA IN PADS                                |    |

|--------------------------------------------|----|

| WIRE BONDABLE SURFACES                     | 47 |

| SURFACE FINISHES DESIGN GUIDELINES         |    |

| ORGANIC SOLDERABILITY PRESERVATIVE (OSP)   |    |

| ELECTROLESS NICKEL / IMMERSION GOLD        |    |

| HOT AIR SOLDER LEVELING (HASL)             |    |

| ELECTROPLATE "TIP PLATING EDGE CONNECTORS" |    |

| CONTROLLED IMPEDANCE                       |    |

| CONTROLLED IMPEDANCE TUTORIAL              |    |

| PRIMARY IMPEDANCE FACTORS                  |    |

| MULTIPLE IMPEDANCE'S                       |    |

| SINGLE-ENDED IMPEDANCE                     |    |

| DIFFERENTIAL IMPEDANCE:                    |    |

|                                            |    |

| CONTROLLED IMPEDANCE DESIGN GUIDELINES     |    |

| CONTROLLED IMPEDANCE MATRIX                |    |

| CONFORMANCE TESTS<br>CONTROLLED GEOMETRY   |    |

| AQL TESTING                                |    |

| 100% TESTING                               |    |

| SERIALIZATION                              |    |

| ELECTRICAL TEST                            |    |

| TESTING TUTORIAL                           |    |

| CONTINUITY TEST                            |    |

| HI-POT TEST                                |    |

| TESTING DESIGN GUIDELINES                  |    |

| CONTINUITY TEST                            |    |

| NETLIST PROGRAMS                           |    |

| HI-POT TEST                                |    |

| PWB DATA REQUIREMENTS                      | 55 |

| PWB DATA REQUIREMENTS TUTORIAL             |    |

| DATA FORMAT                                |    |

| ODB++                                      |    |

| GERBER                                     |    |

| APERTURE WHEELS AND README FILES           |    |

| LAYER NAMING                               |    |

| APERTURE WHEEL AND README FILE EXAMPLE     |    |

| ARRAYS (SUBPANELS)                         |    |

| PWB DATA REQUIREMENTS DESIGN GUIDELINES    |    |

| TRANSMITTING DATA TO HADCO                 |    |

| INTERNET TRANSFER                          |    |

| FTP TRANSFER VIA THE INTERNET              |    |

| MODEM LOGIN                                |    |

| E-MAIL ATTACHMENT                          | 59 |

V1.2

# HADCO

| DATA PACKAGE CONTENT                                         |            |

|--------------------------------------------------------------|------------|

| SPECIFICATIONS                                               | 60         |

| LAYER DATA                                                   | 60         |

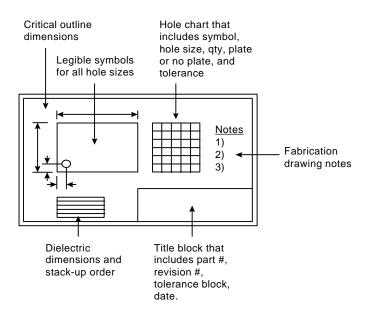

| FABRICATION PRINT                                            | 60         |

| COMMON DATA ISSUES                                           | 61         |

| CRITICAL PROBLEMS                                            |            |

| NON-CRITICAL PROBLEMS                                        |            |

| MANUAL EDITS                                                 |            |

| PRICE CONSIDERATIONS                                         | 63         |

| TURN-AROUND TIME                                             |            |

|                                                              | ( <b>0</b> |

| TECHNICAL ATTRIBUTES                                         |            |

| TECHNICAL ATTRIBUTES<br>HIGH COST FACTORS                    |            |

|                                                              | 63         |

| HIGH COST FACTORS                                            |            |

| HIGH COST FACTORS                                            |            |

| HIGH COST FACTORS<br>MEDIUM COST FACTORS<br>LOW COST FACTORS |            |

# Figures

| FIGURE 1 18" X 24" PANEL EXAMPLE                           | 4   |

|------------------------------------------------------------|-----|

| FIGURE 2 STEP-AND-REPEAT WITHOUT EDGE CONNECTORS           | 5   |

| FIGURE 3 STEP-AND-REPEAT WITH EDGE CONNECTORS              | 6   |

| FIGURE 4 LAY-UP WITH RECESSED EDGE CONNECTORS              | 6   |

| FIGURE 5 CONTROLLED IMPEDANCE COUPON PLACEMENT             | 7   |

| FIGURE 6 ASSEMBLY RAIL DESIGN                              | 7   |

| FIGURE 7 TWO LAYERS (DOUBLE-SIDED)                         | .12 |

| FIGURE 8 FOUR LAYERS                                       | .12 |

| FIGURE 9 SIX LAYERS                                        | .12 |

| FIGURE 10 EIGHT LAYER                                      | .13 |

| FIGURE 11 TEN LAYERS                                       | .13 |

| FIGURE 12 TWELVE LAYERS                                    | .14 |

| FIGURE 13 FOURTEEN LAYERS                                  | .14 |

| FIGURE 14 SIXTEEN LAYERS                                   | .15 |

| FIGURE 15 EIGHT LAYERS (BURIED CAPACITANCE)                | .16 |

| FIGURE 16 TEN LAYERS (BURIED CAPACITANCE).                 |     |

| FIGURE 17 TWELVE LAYERS (BURIED CAPACITANCE)               |     |

| FIGURE 18 LINE WIDTH & SPACING MEASUREMENT.                |     |

| FIGURE 19 SQUARE THIEVING                                  |     |

| FIGURE 20 ANNULAR RING / TANGENCY / BREAKOUT               |     |

| FIGURE 21 PAD-TO-TRACE TEARDROP                            |     |

| FIGURE 22 SAME PAD TO TRACE SPACING                        |     |

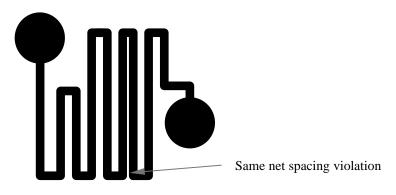

| FIGURE 23 PHOTO RESIST RE-DEPOSIT EXAMPLE                  |     |

| FIGURE 25 SAME NET SPACING.                                |     |

| FIGURE 26 WRONG VECTOR TERMINATIONS                        |     |

| FIGURE 28 AVOID THERMAL ISOLATION & SLIVERS OF COPPER      |     |

| FIGURE 29 CLEARANCE PAD SPACING                            |     |

| FIGURE 30 CLEARANCE PAD PLACEMENT                          |     |

| FIGURE 31 DIRECT CONNECT VIAS.                             |     |

| FIGURE 32 ADJACENT PLANE SEPARATION                        |     |

| FIGURE 33 PLANE CROSSHATCHING.                             |     |

| FIGURE 34 PLANE CROSSHATCHING.                             |     |

| FIGURE 35 CROSSHATCHING EXAMPLE.                           |     |

| FIGURE 36 LOW-PRESSURE FILL EXAMPLE                        |     |

| FIGURE 37 VOID FILL EXAMPLES                               |     |

| FIGURE 38 THERMAL PAD DESIGN                               |     |

| FIGURE 39 HOLE-TO-COPPER SPACING.                          |     |

| FIGURE 40 VIA-TO-GOLD EDGE CONNECTOR SPACING               |     |

| FIGURE 41 SOLDERMASK SMD CLEARANCES                        |     |

| FIGURE 42 SOLDERMASK COVERAGE ON GOLD FINGERS              |     |

| FIGURE 43 SOLDERMASK COVERAGE ON GOLD FINGERS              |     |

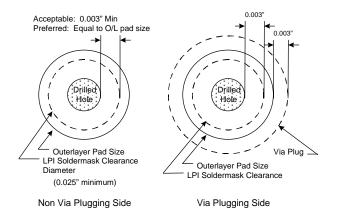

| FIGURE 44 VIA PLUGGING                                     |     |

| FIGURE 45 BREAKAWAY TAB SPACING.                           |     |

| FIGURE 46 BREAKAWAY TAB DETAIL                             |     |

| FIGURE 47 BEVEL DIAGRAM                                    |     |

| FIGURE 48 SCORING DIAGRAM                                  |     |

| FIGURE 49 SCORE COUPON                                     |     |

| FIGURE 50 SCORE COUPON LOCATIONS                           |     |

| FIGURE 51 SELECTIVE GOLD DESIGN RULES                      |     |

| FIGURE 52 VIA TO PAD SPACING                               |     |

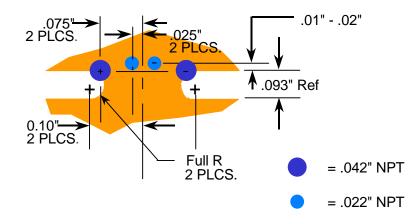

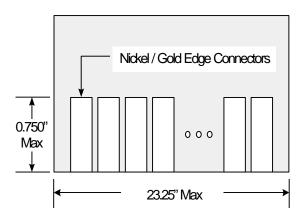

| FIGURE 53 GOLD EDGE CONNECTORS - HEIGHT & WIDTH DIMENSIONS |     |

| FIGURE 54 FABRICAION PRINT REQUIREMENTS.                   |     |

| · · · · · · · · · · · · · · · · · · ·                      |     |

## Tables

| 8  |

|----|

| 10 |

| 10 |

| 11 |

| 11 |

| 11 |

| 12 |

| 35 |

| 51 |

| 52 |

| 61 |

|    |

# INTRODUCTION

Welcome to the HADCO PWB Design for Manufacturability Guidelines. The primary focus of HADCO's mission statement is customer satisfaction. It is our belief that there can be no better way to continually improve customer satisfaction than to offer a more reliable, higher quality, more cost effective circuit board. Some industry analysts believe that 20-25% of a PWB's cost could be avoided if proper consideration were given the manufacturing process. We have seen savings of this magnitude and believe that this may be within your realm of possibility. This document presents volume PWB fabrication design guidelines.

At a basic level, a Printed Wiring board is essentially a solution to an interconnection problem. It is not a commodity product. As such, its value to our customers must be continually enhanced. HADCO believes that a major component in the pursuit of this value enhancement is designing for manufacturability.

There are four factors, which influence the cost of circuit board fabrication more than anything else: material utilization, layer quantity, PWB size and yield. This guide focuses on material utilization, and on factors which affect yield throughout the board fabrication process. The information will help you to design your board as cost effective as possible, without compromising quality or reliability.

HADCO is involved in building leading edge and low to high volume product, both in our Tech Centers and in volume facilities. Technologies include: buried and blind vias, PC cards, thick backplane fabrication and assembly, exotic materials, fine lines, high layer count, tight controlled impedance, and more. We will gladly work with you at length about any challenges that you may have before you.

Product that is designed to these criteria will result in high quality boards with the lowest possible manufacturing costs. The design parameters are applicable for all HADCO volume and Tech Center manufacturing facilities. Additional capabilities are available that are not described in this document. Contact HADCO for more specific information.

The design criteria are provided in two classifications; **Preferred** and **Available**.

**Preferred** criteria will allow the PWB to be manufactured in any volume or Tech Center manufacturing facility.

Available criteria may limit the volume capability to specific manufacturing facilities.

Each section opens with a **tutorial subsection**, which will provide a basic understanding for the subject matter. It will then be followed by **detailed design criteria subsection**, which will provide in-depth specifications and guidelines.

Each HADCO manufacturing facility has unique capabilities. These can be discussed with your Sales or Field Application Engineer representative.

# HADCO SALES AND TECHNICAL SUPPORT LOCATIONS

| Corporate Offices         | 12A Manor Parkway                                 |  |  |

|---------------------------|---------------------------------------------------|--|--|

|                           | Salem, NH 03079                                   |  |  |

|                           | 603-898-8000                                      |  |  |

| Northeast & International | 8C Industrial Way                                 |  |  |

|                           | Salem, NH 03079                                   |  |  |

|                           | 603-898-8000                                      |  |  |

| Mid-Atlantic              | 4000 Vine Street                                  |  |  |

| Whu-Munne                 | Middletown, PA 17057<br>717-944-9560              |  |  |

|                           |                                                   |  |  |

| Southeast                 | 110 Eagle Springs Drive, Suite C                  |  |  |

| Soundast                  |                                                   |  |  |

|                           | Stockbridge, GA 30281<br>770-474-6645             |  |  |

| Latin America             | 4673 NW 97 <sup>th</sup> Court                    |  |  |

| Lutin America             |                                                   |  |  |

|                           | Miami, FL 33178<br>305-436-5434                   |  |  |

| South Central             | 525 International Parkway, Suite 495              |  |  |

| South Central             | Richardson, TX 75081                              |  |  |

|                           | 972-235-1112                                      |  |  |

| South West                | 5020 S. 36 <sup>th</sup> St.                      |  |  |

|                           | 5020 S. 36 <sup>th</sup> St.<br>Phoenix, AZ 85040 |  |  |

|                           | 602-268-3461                                      |  |  |

| North Central             | 5001 W. 80 <sup>th</sup> Street, Suite 495        |  |  |

|                           | Bloomington, MN 55437                             |  |  |

|                           | 612-893-1370                                      |  |  |

| Western                   | 425 El Camino Real                                |  |  |

|                           | Santa Clara, CA 95050                             |  |  |

|                           | 408-241-9900                                      |  |  |

| Canada                    | 5401 Eglinton Ave. W., Suite 204                  |  |  |

|                           | Toronto, Ontario, Canada M9C 5K6                  |  |  |

|                           | 416-626-2020                                      |  |  |

| Asia                      | Pica Centre 20 Kallang Ave.                       |  |  |

|                           | Singapore 339411                                  |  |  |

|                           | (65) 297-0150                                     |  |  |

# HADCO MANUFACTURING AND DESIGN FACILITIES

| III - L X/- L DXVD M                                   | Demma                     | 7 Manahastan Daad                                                                                                                                                                                                                                                    |

|--------------------------------------------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| High Volume PWB Manufacturing                          | Derry                     | 7 Manchester Road                                                                                                                                                                                                                                                    |

|                                                        |                           | Derry, NH 03038                                                                                                                                                                                                                                                      |

|                                                        |                           | 603-432-2004                                                                                                                                                                                                                                                         |

|                                                        | Malaysia                  | Sama-Jaya Free Industrial Zone                                                                                                                                                                                                                                       |

|                                                        |                           | 93450 Kuching, Sarawak Malaysia                                                                                                                                                                                                                                      |

|                                                        |                           | 011-60-82363000                                                                                                                                                                                                                                                      |

|                                                        | Owego                     | 1200 Taylor Road                                                                                                                                                                                                                                                     |

|                                                        |                           | Owego, NY 13827                                                                                                                                                                                                                                                      |

|                                                        |                           | 607-687-3425                                                                                                                                                                                                                                                         |

|                                                        | Phoenix                   | 5020 South 36 <sup>th</sup>                                                                                                                                                                                                                                          |

|                                                        |                           | Phoenix, AZ 85040                                                                                                                                                                                                                                                    |

|                                                        |                           | 602-268-3461                                                                                                                                                                                                                                                         |

|                                                        | Santa Clara               | 435 El Camino Real                                                                                                                                                                                                                                                   |

|                                                        |                           | Santa Clara, CA 95050                                                                                                                                                                                                                                                |

|                                                        |                           | 408-241-9900                                                                                                                                                                                                                                                         |

| <b>Technology Development Centers</b>                  | Tech Center Austin        | 15508 Bratton Lane                                                                                                                                                                                                                                                   |

|                                                        |                           | Austin, TX 78728                                                                                                                                                                                                                                                     |

|                                                        |                           | 512-246-5600                                                                                                                                                                                                                                                         |

|                                                        | Tech Center East          | 46 Rogers Road                                                                                                                                                                                                                                                       |

|                                                        | Teen center Last          | Ward Hill, MA 01835                                                                                                                                                                                                                                                  |

|                                                        |                           | 978-372-0200                                                                                                                                                                                                                                                         |

|                                                        | Tech Center West          | 78 Hangar Way                                                                                                                                                                                                                                                        |

|                                                        | reen center west          | Watsonville, CA 95076                                                                                                                                                                                                                                                |

|                                                        |                           | 408-728-0333                                                                                                                                                                                                                                                         |

| Flex and Rigid Flex                                    | HADCO/Dynaflex            | 1758 Junction Ave., Suite E                                                                                                                                                                                                                                          |

| FICA and Right FICA                                    | TIADCO/Dynanicx           | San Jose, CA 95112                                                                                                                                                                                                                                                   |

|                                                        |                           | 408-441-8717                                                                                                                                                                                                                                                         |

| Value Added Manufacturing (VAM)                        | VAM East                  | 10 Manor Way                                                                                                                                                                                                                                                         |

| value Audeu Manufacturing (VAM)                        | V AIVI Last               | Salem, NH 03079                                                                                                                                                                                                                                                      |

|                                                        |                           | 603-896-2300                                                                                                                                                                                                                                                         |

|                                                        | VAM West                  | 425 El Camino Real                                                                                                                                                                                                                                                   |

|                                                        | VANI WEST                 | Santa Clara, CA                                                                                                                                                                                                                                                      |

|                                                        |                           | ,                                                                                                                                                                                                                                                                    |

|                                                        |                           | 1 408 241 9900                                                                                                                                                                                                                                                       |

| Design Contons                                         | Colorado                  | 408-241-9900<br>2004 West 15 <sup>Th</sup> Street Unit 1                                                                                                                                                                                                             |

| Design Centers                                         | Colorado                  | 2004 West 15 <sup>Th</sup> Street, Unit 1                                                                                                                                                                                                                            |

| <b>Design Centers</b><br>Email: hadco_design@hadco.com | Colorado                  | 2004 West 15 <sup>Th</sup> Street, Unit 1<br>Loveland, CO 80538                                                                                                                                                                                                      |

|                                                        |                           | 2004 West 15 <sup>Th</sup> Street, Unit 1<br>Loveland, CO 80538<br>970-622-8933                                                                                                                                                                                      |

|                                                        | Colorado<br>New Hampshire | 2004 West 15 <sup>Th</sup> Street, Unit 1<br>Loveland, CO 80538<br>970-622-8933<br>8C Industrial Way                                                                                                                                                                 |

|                                                        |                           | 2004 West 15 <sup>Th</sup> Street, Unit 1<br>Loveland, CO 80538<br>970-622-8933<br>8C Industrial Way<br>Salem, NH 03079                                                                                                                                              |

|                                                        | New Hampshire             | 2004 West 15 <sup>Th</sup> Street, Unit 1<br>Loveland, CO 80538<br>970-622-8933<br>8C Industrial Way<br>Salem, NH 03079<br>603-896-2470                                                                                                                              |

|                                                        |                           | 2004 West 15 <sup>Th</sup> Street, Unit 1<br>Loveland, CO 80538<br>970-622-8933<br>8C Industrial Way<br>Salem, NH 03079<br>603-896-2470<br>1915 North Austin Avenue                                                                                                  |

|                                                        | New Hampshire             | 2004 West 15 <sup>Th</sup> Street, Unit 1<br>Loveland, CO 80538<br>970-622-8933<br>8C Industrial Way<br>Salem, NH 03079<br>603-896-2470<br>1915 North Austin Avenue<br>Georgetown, TX 78626                                                                          |

|                                                        | New Hampshire<br>Texas    | 2004 West 15 <sup>Th</sup> Street, Unit 1<br>Loveland, CO 80538<br>970-622-8933<br>8C Industrial Way<br>Salem, NH 03079<br>603-896-2470<br>1915 North Austin Avenue<br>Georgetown, TX 78626<br>512-930-2233                                                          |

|                                                        | New Hampshire             | 2004 West 15 <sup>Th</sup> Street, Unit 1<br>Loveland, CO 80538<br>970-622-8933<br>8C Industrial Way<br>Salem, NH 03079<br>603-896-2470<br>1915 North Austin Avenue<br>Georgetown, TX 78626<br>512-930-2233<br>1821 Saratoga Avenue, Suite 280                       |

|                                                        | New Hampshire<br>Texas    | 2004 West 15 <sup>Th</sup> Street, Unit 1<br>Loveland, CO 80538<br>970-622-8933<br>8C Industrial Way<br>Salem, NH 03079<br>603-896-2470<br>1915 North Austin Avenue<br>Georgetown, TX 78626<br>512-930-2233<br>1821 Saratoga Avenue, Suite 280<br>Saratoga, CA 95070 |

|                                                        | New Hampshire<br>Texas    | 2004 West 15 <sup>Th</sup> Street, Unit 1<br>Loveland, CO 80538<br>970-622-8933<br>8C Industrial Way<br>Salem, NH 03079<br>603-896-2470<br>1915 North Austin Avenue<br>Georgetown, TX 78626<br>512-930-2233<br>1821 Saratoga Avenue, Suite 280                       |

# PANEL UTILIZATION

# PANEL UTILIZATION TUTORIAL

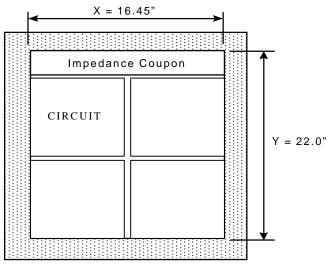

Panelization is the process of positioning one or more Printed Wiring boards (PWB's) on a manufacturing panel and incorporating features to facilitate manufacturing (such as tooling holes, fiducials, coupons, resin vents, panel theiving, etc.). This is one of the highest cost impact factors.

The panel area is divided between these functions:

- Keep-out zones that are required for manufacturing

- Circuit boards (single and arrays)

- Test coupons (such as impedance coupons)

- Circuit board spacing for routing or scoring (depanelization)

- Traces (buss bar traces) added for electroplated edge connectors

The panel area that is available for circuit boards and coupons is called the useable area. The useable area is measured as a percentage (total area for PWB's divided by the total panel area). PWB's are laid out in the useable area, and any area outside the useable area is designated for tooling to optimize manufacturing. A target panel utilization of greater than 70% is considered cost effective material utilization (i.e., lower cost). In order to reduce cost and minimize the amount of unused base material, HADCO offers several manufacturing panel sizes.

Figure 1 18" x 24" panel example

The following pages will outline the provisions and requirements necessary to best utilize the useable area.

Four general panel modifications reduce the available useable area. These modifications are:

- (1) Step-and-repeat requirements

- (2) Assembly rails

- (3) Provisions for electroplating edge connectors

- (4) Coupon requirements

#### **Step-and-repeat**

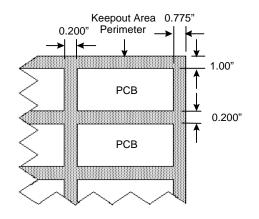

The term 'step-and-repeat' describes the process of reproducing successive images onto a panel. For printed wiring boards without gold-plated edge contacts, the standard step-and-repeat spacing between parts is normally 0.100" to 0.200". A typical lay-up is shown in the following figure.

Figure 2 Step-and-repeat without Edge Connectors

#### **Gold-Electroplated Edge Connectors**

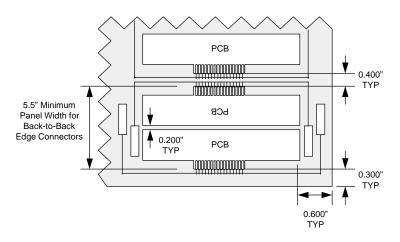

For Printed Wiring boards with gold-plated edge connectors (a.k.a. tips, fingers, tabs), parts are usually arranged such that the edge connectors are either facing each other or opposite each other when plated on a tip plating line. When the edge connectors are facing each other, the spacing between the part outlines needs to be at least 0.400" minimum. This allows space for tie bars to connect to the connectors for electroplating and to allow room for a shearing operation to separate the pieces. When the edges opposite the edge connectors are facing each other, the space between the parts can be 0.200" since there is no gold plating required in this area.

Figure 3 Step-and-repeat with edge connectors

For Printed Wiring boards with recessed gold-plated edge connectors, the same rules apply as those without recessed edge connectors. Panels, which contain edge connectors that can not be plated on the tip plating line, can be plated in the deep gold plating lines that are available at several HADCO facilities.

Figure 4 lay-up with recessed edge connectors

#### **Controlled Impedance Coupons**

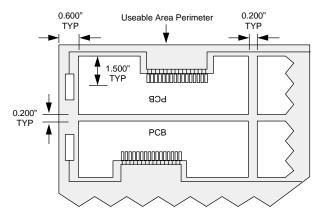

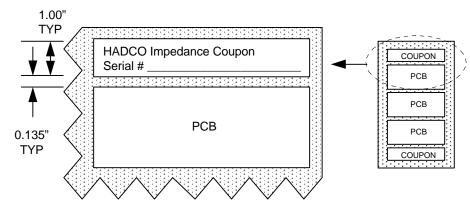

Printed Wiring boards with controlled impedance technology are processed with test coupons as part of the lay-up. When a +/- 10% of nominal impedance tolerance is specified, we recommend using controlled geometry versus controlled impedance (see Controlled Impedance section). This will free area on the panel for parts since the coupons will not be required. It also may allow a smaller panel size to be used. The coupons are typically one-inch wide and are placed along the short end of the panel. A typical arrangement is shown in the following figure.

Figure 5 Controlled impedance coupon placement

#### **Assembly Rails**

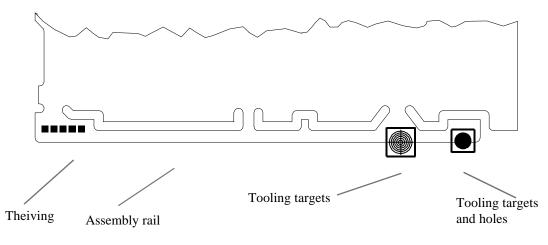

To maximize the number up on a panel when assembly rails are required, the following should be considered. A minimum of a 1.0" border must be maintained around the perimeter of the panel to allow for HADCO's pinning, coupons, plating clamps, and other assorted targets that are required to tool a panel. It is a common practice for the assembly rail (breakaway) to enter the 0.5" border of the panel, keeping the PWB away from the border. When the rail enters the 0.5" border of the panel, some HADCO tooling features may remain on the rail after processing. This can include, tooling holes, targets, inner layer gates and theiving. These additional features do not generally affect any assembly operations.

Figure 6 Assembly rail design

#### Assembly arrays or sub-panels

PWB's are often required to be step-and-repeated onto an array for assembly. The assembly array database should be provided to HADCO to ensure that the correct array is provided to the assembler.

## PANEL UTILIZATION DESIGN GUIDELINES

|                           | KEY REQUIREMENTS |                                                                                                                                                                                                             |

|---------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Specification<br>General: | Preferred        | Available / Special Options:                                                                                                                                                                                |

| Panel sizes: (inches)     | 18 x 24          | 12 x 18, 12 x 21, 12 x 24, 12 x 27,<br>14 x 16, 14 x 18, 14 x 21, 14 x 24, 14 x 27,<br>16 x 18, 16 x 21, 16 x 24, 16 x 27,<br>18 x 21, 18 x 26, 18 x 27, 19 x 25<br>20 x 21, 21x24, 21 x 25, 21x27, 22 x 24 |

## STANDARD PANEL SIZES

Use the following table to determine the maximum, single 1-up PWB's that can fit into a panel. The 18"x24" panel is preferred because it is the most common panel size in the industry. The PWB dimensions should be optimized to maximize the panel utilization. This will provide the most real estate for circuitry and component mounting.

| Panel Sizes | Useable Area | Panel Sizes | Useable Area  |

|-------------|--------------|-------------|---------------|

| (mm)        | (mm)         | (in)        | (in)          |

| 305 X 457   | 265 X 406    | 12 X 18     | 10.45 X 16    |

| 305 X 533   | 265 X 482    | 12 X 21     | 10.45 X 19    |

| 305 X 610   | 265 X 305    | 12 X 24     | 10.45 X 22    |

| 355 X 406   | 316 X 355    | 14 X 16     | 12.45 X 14    |

| 355 X 457   | 316 X 406    | 14 X 18     | 12.45 X 16    |

| 355 X 533   | 316 X 482    | 14 X 21     | 12.45 X 19    |

| 355 X 610   | 316 X 559    | 14 X 24     | 12.45 X 22    |

| 355 X 686   | 316 X 635    | 14 X 27     | 12.45 X 25    |

| 406 X 457   | 367 X 406    | 16 X 18     | 14.45 X 16    |

| 406 X 533   | 367 X 482    | 16 X 21     | 14.45 X 19    |

| 406 X 610   | 367 X 559    | 16 X 24     | 14.45 X 22    |

| 406 X 686   | 367 X 635    | 16 X 27     | 14.45 X 25    |

| 457 X 533   | 417 X 482    | 18 X 21     | 16.45 X 19    |

| 457 X 610   | 417 X 559    | 18 X 24     | 16.45 X 22    |

| 457 X 660   | 417 X 610    | 18 X 26     | 16.45 X 24    |

| 457 X 686   | 417 X 635    | 18 X 27     | 16.45 X 25    |

| 482 X 635   | 423 X 594    | 19 X 25     | 17.025 X 23.4 |

| 508 X 533   | 468 X 482    | 20 X 21     | 18.45 X 19    |

| 533 X 610   | 494 X 559    | 21 X 24     | 19.45 X 22    |

| 533 X 635   | 494 X 584    | 21 X 25     | 19.45 X 23    |

| 533 X 686   | 496 X 640    | 21 X 27     | 19.55 X 25.2  |

| 610 X 711   | 570 X 610    | 24 X 28     | 22.45 X 26    |

Table 1 Panel sizes & useable area

# MATERIALS AND LAYER STACKUP

# MATERIALS & LAYER STACKUP TUTORIAL

#### Materials

HADCO generally manufactures PWB's using Epoxy-glass (FR-4) dielectrics and copper foil. PWB's are constructed from three basic material types; Copper foil, prepreg and cores.

- **Copper foil**: Sheets of copper foil are incorporated into the outer layer of the PWB placing it on the prepreg to create the outer layers. Outer layers are generally constructed using 0.5 oz. copper. Internal layers are constructed with copper that is specified on the fabrication print. 1 oz. foil is generally preferred. 0.5 oz. is commonly used for signal layers with fine lines. 2 oz. copper is used for power planes where there is a high DC current.

- **Prepreg**: This is commonly called B-stage. This is semi-cured glass-epoxy material. There is no copper attached to this material.

- **Core**: This is commonly called C-stage. This is fully-cured glass-epoxy material with copper laminated to both sides. This is used for internal layers. It is occasionally used for outer layers, but is not preferred. A core is constructed of one (single-ply) or two (or more plies of two-ply) prepreg layer and two layers of copper foil. Single ply is considered the preferred core construction and has better dimensional stability.

More exotic board materials are available and are discussed in the Advanced Technologies section. Combinations of glass-epoxy and exotic materials can provide cost effective, high performance PWB's.

#### Layer Stackup

Layer stackups are determined by mechanical and electrical requirements. This information is detailed on the PWB Fabrication drawing. Only the key mechanical attributes should be specified. These are generally:

- Overall PWB thickness and tolerance

- Measurement reference locations (copper to copper, glass to glass, etc.)

- Impedance

- Critical layer-to-layer spacing (and tolerance)

HADCO prefers to use Foil versus all Core constructions. This is the most cost-effective approach because both sides of the adjacent internal layers are imaged and etched together. This improves productivity and yield. The outer layer circuitry is not created until after drilling.

The following guidelines should be used when determining multilayer constructions:

- To promote even etch distribution and minimize warp & twist, design balanced constructions that are symmetrical from the lay-up's center outward.

- Whenever possible, only one core thickness should be used.

- Actual layer-to-layer spacing will vary based on whether each side has signal or power planes and the copper weight used for those layers.

- The overall board thickness should not be specified less than +/- 10%.

- Boards that are thicker than 0.100" and have more than eight layers should utilize high Tg material when utilized in high operating temperature environments or in high availability or reliability application. This will lower the PWB Z-exis thermal expansion rate and create a more reliable PTH's.

- Specify how the overall board thickness should be measured. For example specify that it should be measured over copper or over laminate. Edge connector boards should be measured over copper to ensure that the correct insertion thickness is obtained.

- Single ply construction should be allowed.

- Cores should have the same copper weight on both sides to ensure good trace etching tolerance.

## MATERIAL DESIGN GUIDELINES

| KEY REQUIREMENTS                    |                                |                                     |  |

|-------------------------------------|--------------------------------|-------------------------------------|--|

| Specification                       | Preferred                      | Available / Special Options:        |  |

| Materials:                          |                                |                                     |  |

| Laminate types available:           | FR-4 (Tg = 135°C minimum)      | FR-4 (Tg = $170^{\circ}$ C minimum) |  |

| Foil weight: (inner layer)          | 1/2, 1 ounce                   | 2,3 ounce                           |  |

| Foil weight: (outer layer)          | 1/2 ounce                      | 1 ounce                             |  |

| Dielectric & PWB thickness :        |                                |                                     |  |

| Minimum overall board thickness:    | 0.031"                         | 0.016"                              |  |

| (As measured over metal)            |                                |                                     |  |

| Maximum overall board thickness:    | 0.150"                         | 0.250"                              |  |

| (As measured over metal)            |                                |                                     |  |

| Thickness tolerance:                | +/- 10%                        | +/- 8%                              |  |

| Warp and Twist                      | 1%                             | 0.7%, 0.5%                          |  |

| Minimum dielectric spacing:         | Cores: 0.005" Prepregs: 0.004" | Cores: 0.002" Prepregs: 0.004"      |  |

| Minimum PC Card dielectric spacing: | Cores: 0.002" Prepregs: 0.002" |                                     |  |

#### **FR4 Material Tolerances**

| THICKNESS RANGE<br>(inches) | TOLERANCE<br>(inches) |

|-----------------------------|-----------------------|

| 0.0020 to 0.0069            | +/- 0.0005            |

| 0.0070 to 0.0099            | +/- 0.0007            |

| 0.0100 to 0.0139            | +/- 0.0010            |

| 0.0140 to 0.0209            | +/- 0.0020            |

| 0.0210 to 0.0339            | +/- 0.0025            |

| 0.0340 to 0.0560            | +/- 0.0040            |

| Table 2 FR4 laminate | (core) tole | rances |

|----------------------|-------------|--------|

|----------------------|-------------|--------|

| THICKNESS RANGE<br>(inches) | TOLERANCE<br>(inches) |

|-----------------------------|-----------------------|

| 0.0010 to 0.0029            | +/- 0.0003            |

| 0.0030 to 0.0074            | +/- 0.0005            |

| 0.0075 to 0.0109            | +/- 0.0010            |

| 0.0110 to 0.0139            | +/- 0.0015            |

| 0.0140 to 0.0199            | +/- 0.0020            |

| 0.0200 to 0.0299            | +/- 0.0025            |

Table 3 FR4 laminate prepreg tolerances

| MULTI-PLY GLASS STYLES | SINGLE PLY STYLES |

|------------------------|-------------------|

| 1060                   | 6000              |

| 1080                   | 8000              |

| 2113                   |                   |

| 2116                   |                   |

| 7628                   |                   |

#### Table 4 FR4 glass styles

| COPPER WEIGHT<br>(ounce) | THICKNESS<br>(inches) | THICKNESS<br>(microns) |

|--------------------------|-----------------------|------------------------|

| 0.5                      | 0.00050               | 20                     |

| 1                        | 0.00120               | 48                     |

| 2                        | 0.00260               | 104                    |

Table 5 Copper foil thickness (after processing)

| Material Type | Transition Temperature |

|---------------|------------------------|

| Standard FR4  | ≥ 130° C               |

| High Tg FR4   | ≥ 160° C               |

Table 6 FR4 Material glass transition temperatures

## MULTILAYER CONSTRUCTION DESIGN GUIDELINES

The following guidelines should be used when designing multilayer constructions:

- Design balanced constructions that are symmetrical from the lay-up's center outward to promote even etch distribution and minimize warp & twist.

- Use only one core thickness whenever possible.

- The maximum B-Stage opening between C-Stages is 0.021".

- High Tg materials should be used in high temperature or high reliability applications.

- Each outer layer is typically a signal layer built using 0.5 ounce copper.

- The overall board thickness should not be specified less than +/-10%.

- Warp and twist should be specified to be  $\geq 1\%$ .

#### **Standard PWB Constructions**

The following examples are the most cost-effective constructions for common 0.062" and 0.093" thick PWB's. These should be used for PWB's where specific layer to layer spacing is not required. Other cost effective PWB thickness' can be calculated for you by HADCO. All measurements are taken over copper. The impedance values for each of these constructions are provided in the Impedance section.

Note: - Constructions are not drawn to scale.

| -All dimensions are in inches/ |  |  |  |

|--------------------------------|--|--|--|

| KEY                            |  |  |  |

| P Power                        |  |  |  |

| G Ground                       |  |  |  |

| S Signal                       |  |  |  |

| LAYER | ТҮРЕ | CONSTRUCTION | CU WEIGHT | OVERALL THICKNESS |

|-------|------|--------------|-----------|-------------------|

| 1     | S    | 0.0590"      | 0.5       | 0.062 +/006"      |

| 2     | S    |              | 0.5       | 0.002 17 1000     |

#### Figure 7 Two Layers (Double-sided)

| LAYER | TYPE | CONSTRUCTION | CU WEIGHT | OVERALL THICKNESS |

|-------|------|--------------|-----------|-------------------|

| 1     | S    |              | 0.5       |                   |

| 2     | G    | 0.0154"      | 1         |                   |

| 3     | Р    | 0.0230"      | 1         | 0.062 +/006"      |

|       |      | 0.0154"      |           |                   |

| 4     | S    |              | 0.5       |                   |

#### **Figure 8 Four Layers**

| LAYER | TYPE     | CONSTRUCTION | CU WEIGHT | OVERALL THICKNESS |

|-------|----------|--------------|-----------|-------------------|

| 1     | S        |              | 0.5       |                   |

|       |          | 0.0063"      |           |                   |

| 2     | G        |              | 1         |                   |

|       | _        | 0.0140"      |           |                   |

| 3     | S        |              | 1         |                   |

| 4     | <u> </u> | 0.0110"      | 4         | 0.062 +/006"      |

| 4     | S        | 0.0140"      | 1         |                   |

| 5     | Р        |              | 1         |                   |

| Ŭ     | 1        | 0.0063"      | ,         |                   |

| 6     | S        |              | 0.5       |                   |

Figure 9 Six Layers

| LAYER | TYPE | CONSTRUCTION | CU WEIGHT | OVERALL THICKNESS |

|-------|------|--------------|-----------|-------------------|

| 1     | S    |              | 0.5       |                   |

| 2     | S    | 0.0055"      | 1         |                   |

| 3     | G    | 0.0081"      | 1         |                   |

| 4     | S    | 0.0072"      | 1         |                   |

| 5     | S    | 0.0081"      | 1         | 0.062 +/006"      |

|       |      | 0.0072"      | 1         |                   |

| 6     | P    | 0.0081"      | ŗ         |                   |

| 7     | S    | <br>0.0055"  | 1         |                   |

| 8     | S    |              | 0.5       |                   |

#### Figure 10 Eight Layer

| LAYER | TYPE | CONSTRUCTION | CU WEIGHT | OVERALL THICKNESS |

|-------|------|--------------|-----------|-------------------|

| 1     | S    |              | 0.5       |                   |

|       | -    | 0.0046"      |           |                   |

| 2     | G    | 0.0055"      | 1         |                   |

| 3     | S    | 0.0055       | 1         |                   |

|       |      | 0.0045"      |           |                   |

| 4     | S    |              | 1         |                   |

| 5     | Р    | 0.0055"      | 1         |                   |

| Ű     | ·    | 0.0060"      |           | 0.062 +/006"      |

| 6     | G    |              | 1         |                   |

| 7     | S    | 0.0055"      | 1         |                   |

| /     | 3    | 0.0045"      | I         |                   |

| 8     | S    |              | 1         |                   |

|       | _    | 0.0055"      |           |                   |

| 9     | Р    | 0.0046"      | 1         |                   |

| 10    | S    |              | 0.5       |                   |

Figure 11 Ten Layers

| LAYER | ТҮРЕ | CONSTRUCTION                        | CU WEIGHT         | OVERALL THICKNESS |

|-------|------|-------------------------------------|-------------------|-------------------|

| 1     | S    | 0.0062"                             | 0.5               |                   |

| 2     | G    | 0.0063"                             | 1                 |                   |

| 3     | S    | 0.0071"                             | 1                 |                   |

| 4     | S    | 0.0065"                             | 1                 |                   |

| 5     | Р    | 0.0071"                             | 1                 |                   |

| 6     | S    | 0.0072"                             | 1                 |                   |

| 7     | S    | 0.0071"                             | 1                 | 0.093 +/009"      |

| 8     | G    | 0.0072"                             | 1                 |                   |

| 9     | S    | 0.0071"                             | 1                 |                   |

| 10    | S    | 0.0065"                             | 1                 |                   |

|       |      | 0.0071"                             |                   |                   |

| 11    | P    | 0.0063"                             | 1                 |                   |

| 12    | S    |                                     | 0.5               |                   |

| LAYER | ТҮРЕ | Figure 12 Twelve La<br>construction | yers<br>CU WEIGHT | OVERALL THICKNESS |

| 1     | S    |                                     | 0.5               |                   |

| 2     | S    | 0.0055"                             | 1                 |                   |

| 3     | G    | 0.0059"                             | 1                 |                   |

| 4     | S    | 0.0053"                             | 1                 |                   |

|       |      | 0.0059"                             |                   |                   |

| 5     | S    | 0.0053"                             | 1                 |                   |

| 6     | Р    | 0.0059"                             | 1                 |                   |

| 7     | S    | 0.0045"                             | 1                 | 0.093 +/009"      |

| 8     | S    | 0.0059"                             | 1                 |                   |

| 9     | G    | 0.0053"                             | 1                 |                   |

| 10    | S    | 0.0059"                             | 1                 |                   |

| 11    | S    | 0.0053"                             | 1                 |                   |

| 12    | Ρ    | 0.0059"                             | 1                 |                   |

| 13    | S    | 0.0055"                             | 1                 |                   |

| 14    | S    | 0.0000                              | 0.5               |                   |

Figure 13 Fourteen Layers

| LAYER | TYPE | CONSTRUCTION | CU WEIGHT | OVERALL THICKNESS |

|-------|------|--------------|-----------|-------------------|

| 1     | S    |              | 0.5       |                   |

| 2     | G    | 0.0049"      | 1         |                   |

| 3     | S    | 0.0045"      | 1         |                   |

|       |      | 0.0045"      |           |                   |

| 4     | S    | 0.0045"      | 1         |                   |

| 5     | Р    | 0.0053"      | 1         |                   |

| 6     | S    | 0.0045"      | 1         |                   |

| 7     | S    |              | 1         |                   |

| 8     | G    | 0.0053"      | 1         |                   |

| 9     | Р    | 0.0045"      | 1         | 0.093 +/009"      |

|       |      | 0.0053"      |           |                   |

| 10    | S    | 0.0045"      | 1         |                   |

| 11    | S    | 0.0053"      | 1         |                   |

| 12    | G    | 0.0045"      | 1         |                   |

| 13    | S    |              | 1         |                   |

| 14    | S    | 0.0045"      | 1         |                   |

| 15    | Р    | 0.0045"      | 1         |                   |

| 16    | S    | 0.0049"      | 0.5       |                   |

| 10    | 5    |              | 0.5       |                   |

Figure 14 Sixteen Layers

# BURIED CAPACITANCE<sup>™</sup> DESIGN GUIDELINES

#### **Capacitance without Capacitors**

Printed Wiring board design is a tug-of-war between maximizing performance and minimizing cost. Conventional wisdom says when you achieve one you sacrifice the other. But a new technology takes a big step towards refuting this notion by enabling engineers to improve high frequency EMI performance and system quality while reducing the impact on system cost.

Patented and licensed worldwide, Buried Capacitance<sup>TM</sup> (BC), utilizes ZBC-2000<sup>TM</sup> laminate. It is an advanced board manufacturing technique in which distributed decoupling capacitance is achieved by embedding thin dielectric layers within the board between adjacent power planes. This technique makes virtually all discrete decoupling capacitors unnecessary, thereby clearing the board space and enabling designers to design boards that can have greater functionality or a reduced size. More detailed design information can be obtained from the "Buried Capacitance Design Guide".

#### **Preferred Buried Capacitance Constructions**

The following figures present common Buried Capacitance constructions. Please consult the Buried Capacitance Design Guide for specifics on power and ground plane orientation. The most common sequences are shown in the following figures.

|   |   | KEY                |                                           |              |

|---|---|--------------------|-------------------------------------------|--------------|

|   |   | P<br>G<br>S<br>LYR | Power<br>Ground<br>Signal<br>Layer Number |              |

| 1 | S | 0.0063"            | 0.5                                       |              |

| 2 | G | 0.002"             | 1                                         |              |

| 3 | Ρ | 0.0072"            | 1                                         |              |

| 4 | S | 0.0018"            | 1                                         | 0.062 +/006" |

| 5 | S | 0.0072"            | 1                                         |              |

| 6 | G | 0.002"             | 1                                         |              |

| 7 | Р | 0.0063"            | 1                                         |              |

| 8 | S |                    | 0.5                                       |              |

-All dimensions are in inches

Figure 15 Eight Layers (Buried Capacitance)

| 1  | S | 0.0063" | 0.5 |              |

|----|---|---------|-----|--------------|

| 2  | G |         | 1   |              |

| 3  | Р | 0.0020" | 1   |              |

| 4  |   | 0.0053" | 1   |              |

| 4  | S | 0.0071" | 1   |              |

| 5  | S | 0.0045" | 1   | 0.062 +/006" |

| 6  | S |         | 1   | 0.002 +/000  |

| 7  | S | 0.0071" | 1   |              |

|    |   | 0.0053" | 4   |              |

| 8  | G | 0.0020" | 1   |              |

| 9  | Р | 0.0063" | 1   |              |

| 10 | S |         | 0.5 |              |

Figure 16 Ten Layers (Buried Capacitance)

| 1    | S | 0.0049" | 0.5 |              |

|------|---|---------|-----|--------------|

| 2    | G |         | 1   |              |

| 3    | Р | 0.0020" | 1   |              |

|      |   | 0.0039" | I   |              |

| 4    | S | 0.0049" | 1   |              |

| 5    | S |         | 1   |              |

| 6    | G | 0.0039" | 1   |              |

| Ū    |   | 0.0049" | I   | 0.062 +/006" |

| 7    | Р | 0.0039" | 1   |              |

| 8    | S |         | 1   |              |

| 9    | S | 0.0049" | 1   |              |

|      |   | 0.0039" |     |              |

| 10   | G | 0.0020" | 1   |              |

| 11   | Р |         | 1   |              |

| 12   | S | 0.0049" | 0.5 |              |

| 1 12 | 3 |         | 0.0 |              |

Figure 17 Twelve Layers (Buried Capacitance)

# TRACES, PADS & CONDUCTIVE FEATURES

# TRACES, PADS & CONDUCTIVE FEATURES TUTORIAL

#### Line width and space

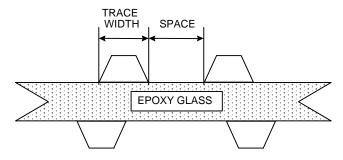

Figure 18 Line width & spacing measurement

The required line width and space is established in the provided CAD database. The line width should be measured at the base of the trace. This is much easier to measure and is provides a more repeatable measurement. The CAM database will be modified to compensate the trace width of the production artwork for the manufacturing processes.

Inner layer features are easier to reproduce, than outer layer features. Inner layer features are exposed to less processing steps than outer layer features.

#### Thieving

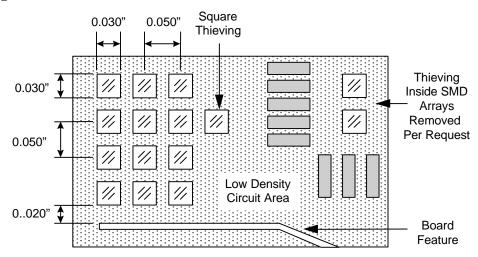

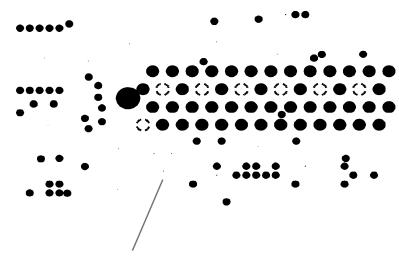

#### **Figure 19 Square Thieving**

Outer layer copper features are created by imaging a base pattern and plating copper to a specified thickness. The pattern plating process is very dependent on the uniformity of the copper features on the outer layers. Areas that have a very small amount of copper (like isolated single traces) will plate a very thick amount of copper on those features. Other areas that have uniform density will have a plating thickness that will be within the specified thickness. Non-functional thieving pads can be added to low-density areas to even out the copper distribution. This is called thieving. Thieving should be incorporated

during the PWB layout to ensure that you will receive identical coverage from all suppliers. HADCO can also automatically thieve the inner and outer layers with our CAM system.

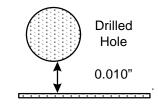

#### Pads, drilled holes and power plane clearance

The drilled hole to power plane distance is critical to ensure that the plating in the hole will not short to adjacent traces or planes.

A plated thru hole connects to traces through a pad. Pads may connect to one or more traces. The target pad and drilled hole have manufacturing tolerances associated with them. The following equation is used to calculate the required pad size based on a drilled hole size:

Pad diameter = Drilled hole diameter + 2 x (annular ring) + manufacturing tolerance

| Drilled hole diameter   | = This will be discussed in the next section                      |

|-------------------------|-------------------------------------------------------------------|

|                         | = Finished nominal hole size + plating manufacturing compensation |

| Annular ring            | = The distance between the drilled hole and edge of pad           |

| Manufacturing tolerance | = Pad etching and drilled hole locational tolerance               |

#### EXAMPLE:

The design requires a 0.038" +/- .003" finished plated through hole with a 0.001" annular ring. What pad diameter should be used for the inner and outer layers?

```

Outer layer pad diameter = (0.038" + 0.005") + 2 \ge (0.001") + 0.010"

= 0.055"

Inner layer pad diameter = (0.038" + 0.005") + 2 \ge (0.001") + 0.012"

= 0.057"

```

The clearance between the hole and the power plane is essential to ensure that the plating in the through hole does not wick along fiberglass bundles and short to the plane. The power plane clearance is determined from the following equation.

Plane Clearance = Drilled hole diameter + 2x (annular ring) + 2x (power plane clearance)

#### EXAMPLE:

The design requires a  $0.038^{\circ}$  +/-  $.003^{\circ}$  finished plated through hole with a  $0.001^{\circ}$  annular ring. The specification requires a  $0.010^{\circ}$  pad to plane clearance and is using an OSP surface finish. What power plane clearance anti-pad should be used?

Power plane clearance =  $(0.038" + .005") + 2 \times (0.001") + 2 \times (0.010")$ = 0.065"

#### **Annular Ring**

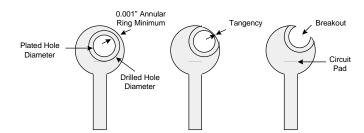

Figure 20 Annular Ring / Tangency / Breakout

Annular ring specifies the distance between the worst case drilled hole to pad distance. This can be specified with a finite distance. It can also be specified as tangent to, or the hole may breakout of the pad. Non-critical hole to trace areas should allow the holes to have a 25% breakout. Critical hole to trace distances should be specified to be tangent.

The manufacturing tolerance will be smaller for outer layers than for inner layers. This is because the outer layer image is registered to the actual drilled holes.

#### Non-functional pad removal

Pads that do not connect to traces are not required on inner layers. They should be removed to increase drill life (reduce drill cost). This is called non-functional pad removal. Removal of the unused pads will not affect the board reliability. Non-functional pad removal should be specified on the fabrication drawing or specification.

#### Teardropping

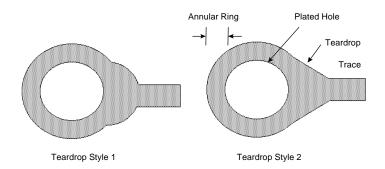

Figure 21 Pad-to-trace teardrop

The drilled hole may finish tangent to the side of the pad where the trace connects to the pad. An extension to the pad should be added at the trace to pad intersection to ensure that the hole will not create a possible open at this point. This is called teardropping. The teardrop addition should extend 0.005" onto the trace.

#### **Circuit to pad connections**

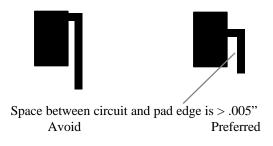

The preferred method of connecting a circuit to a pad is to have the vector enter the pad terminating at the center of the pad without any bends or turns while it is in the pad. If the pad is square it is preferred that the circuit does not run along the side of the pad, 0.001" or 0.002" mils from the pad, and then enter at the center of the pad.

It is also possible to have the circuit run up the side of a square pad and enter at the center, but the distance between the circuit and the side of the pad should be equal to the nominal spacing of the layer.

Figure 22 Same pad to trace spacing

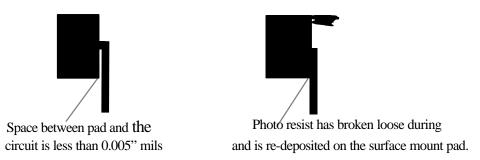

If the same net spacing is less then 4 mils along the edge of a surface mount pad, it can cause excessive amounts of design rule violations and processing problems like, flaking resist that will re-deposit causing pin holes, damaged SMD pads or cut circuits.

It is not a good design practice when the circuits do not enter on the center axis of a round pad, but this can cause flares to be off center and cause false errors in the design rule checks, spacing problems, and possibly shorts.

Figure 24 Off-center trace connections to a round pad

#### **Dangling Traces**

Trace segments that stub from a pad or trace that do not connect to another pad are called dangling traces. These cause problems during the manufacturing process because they look like a broken trace. These cause false errors during manufacturing. These should be removed during the post rout clean up. We will ask to remove these during the CAM process.

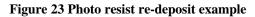

#### Spacing

Feature to feature spacing should be considered between all copper features. This includes:

- Hole to pad

- Pad to pad

- Pad to trace

- Trace to trace (same net and different nets)

- Hole to hole

- PWB edge to copper

In some designs same net spacing violations can cause functional problems.

Figure 25 Same net spacing

Spacing design rule checks should not allow same net spacing violations to pass.

#### Line widths

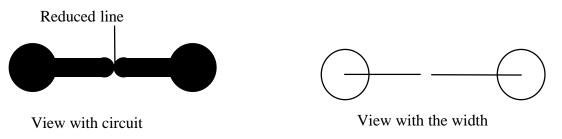

Circuits should be drawn with one vector that terminates at another vector or at a pad. Circuits drawn with more than one vector, which do not terminate together, can result in reduced line widths. These types of line width reductions can not be caught with our design rule checks.

Figure 26 Wrong vector terminations

The width of circuits should be defined by 1 vector and not drawn with 2 or more. This will prevent false errors while running the design rule checks.

Figure 27 Correct vector terminations

#### Power plane clearance and thermal pads

Sufficient clearance (anti-pad) must be provided between a pad and the internal power planes to ensure that copper plating from the via won't provide a conduit which can create a short circuit.

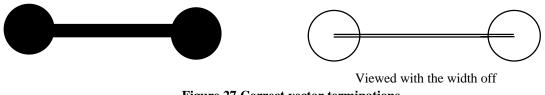

Figure 28 Avoid thermal isolation & slivers of copper

Thermal relief pads patterns should provide a long and wide enough spoke to ensure that all spokes are connected. Care should be taken to ensure that power planes areas do not become isolated after the thermal relief pads are placed and etched. Small slivers of copper should be removed. These may flake during fabrication and create shorts in another location when they re-deposit on a layer. The designer should be sure to check these in the CAD system prior to releasing the final design.

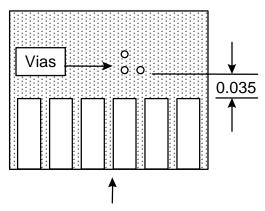

#### **Clearance Pads**

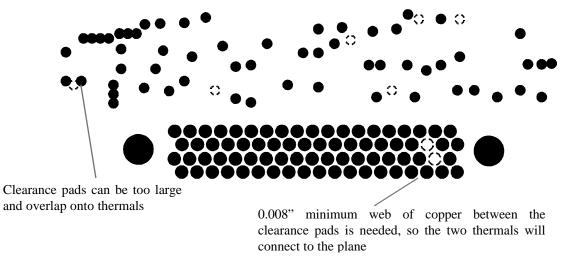

Clearance pads (anti-pads) keep the plane away from the plated through hole to ensure that the copper plating does not wick along glass fibers between the hole and plane. This wicking can create a short circuit between the hole and plane after many hours of operation due to CAF. This function is called electro-migration.

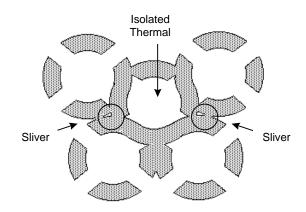

Clearance sizes that are too large can cause areas between clearances to have webs, or residues of less than 0.005". Small webs can break loose, dangle or redeposit and enter a clearance during the inner layer process and cause shorts.

Small residues between clearances of less than 0.005"

#### Figure 29 Clearance pad spacing

Clearance pads that may surround a thermal must maintain a minimum web between them to maintain a connection, after etch, between the surrounded thermal and the rest of the plane.

**Figure 30 Clearance pad placement**

#### Direct connect vias (No thermal pad)

Direct connection of holes to a plane should include a clearance anti-pad half of the diameter of the hole placed at these locations. This will reduce the amount of copper that needs to be drilled, and will result in less drill breakage of smaller drills.

Clearance pads added half of the diameter of the vias

Figure 31 Direct connect vias

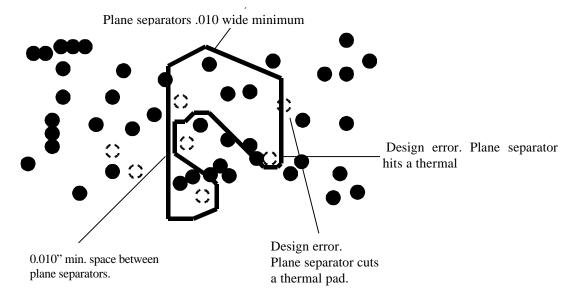

#### Voltage plane separation

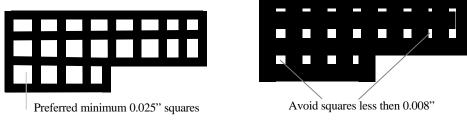

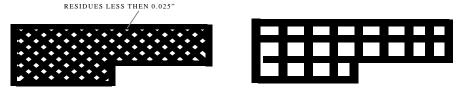

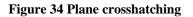

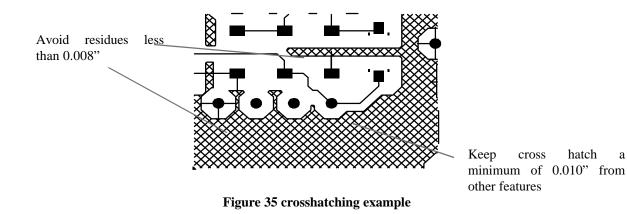

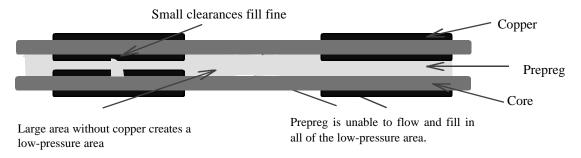

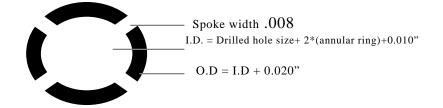

Voltage plane separation on the same plane (split planes) should be sufficient to ensure that electrical properties are maintained. The spacing should be no closer than 0.010".